双芯片封装,是将两个集成电路封装在一起的技术;多芯片封装(MCP),是将三个或三个以上集成电路封装在一起的技术。双/多芯片封装可以在缩小芯片面积的同时提高芯片功能集成度,是一种先进3D封装技术,不是简单的两个或多个芯片堆叠,对封装工艺提出更高要求。

目前,5nm工艺制程芯片已经进入量产阶段,台积电计划2022年9月量产3nm芯片,2025年量产2nm芯片,不久的将来,1nm芯片量产成为可能。发展到此阶段,芯片功能开发已经达到物理极限,摩尔定律失效,但处理器与存储器的运算速度与存储容量要求还在不断提升,二者冲突下,必须依靠新的工艺技术来提高芯片性能,改进封装工艺成为重要路径之一。

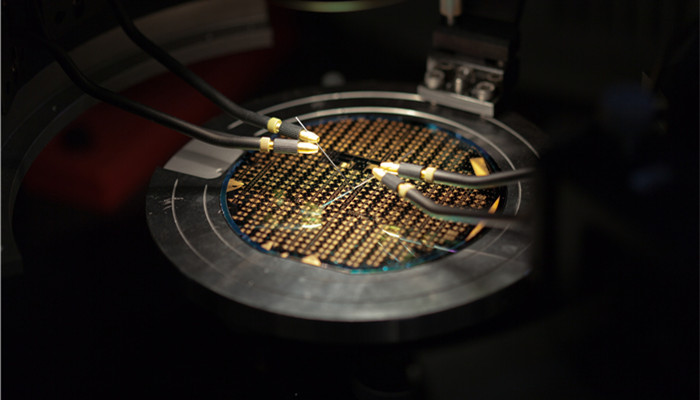

双/多芯片封装是3D封装工艺,可以纵向立体堆叠芯片进行封装,提高芯片功能集成度。由于无需在一个平面上分布更多微电子元件,双/多芯片封装可以缩小芯片面积,并提高产品良率。因此,在摩尔定律失效、芯片性能要求提高冲突下,双/多芯片封装成为重要解决方案之一,受到众多半导体厂商关注。

双/多芯片封装是将两个或多个芯片,分别安装在相应引线框垫上,引线框与芯片之间采用接合线进行连接,利用固定框,分别将引线框垫固定在封装衬底上。双/多芯片封装需要综合考虑产品的性能、功耗、尺寸、成本、可靠性、使用寿命等参数,并不是简单的将两个芯片或者多个芯片进行堆叠封装,相较于传统封装工艺,其技术壁垒更高。

新思界

行业分析人士表示,2020年3月,美光宣布业界首款LPDDR5 DRAM UFS多芯片封装正式送样;2021年6月,三星发布一款用于5G智能手机的新型多芯片封装内存产品;AMD即将于2022年10月发布采用双芯片封装工艺的RDNA3架构显卡。双/多芯片封装市场空间大,全球相关产品种类正在不断增多,包括中央处理器、存储器、图形处理器等,未来其发展前景广阔。

关键字: